- 1. Verilog 테스트벤치 작성 방법 – 테스트벤치란?

- 2. Verilog 테스트벤치 작성 방법 – 기본적인 테스트벤치 작성 단계

- 3. Verilog 테스트벤치 작성 방법 – 예시 코드

1. Verilog 테스트벤치 작성 방법 – 테스트벤치란?

테스트벤치는 Verilog 코드의 동작을 검증하고 시뮬레이션하기 위해 필요한 파일입니다. 코드가 의도한 대로 동작하는지 확인합니다.

테스트벤치는 실제로 하드웨어로 구현되지 않고, 그저 시뮬레이션 하기 위해 사용되기 때문에 input과 output이 없다는 특징 있습니다.

2. Verilog 테스트벤치 작성 방법 – 기본적인 테스트벤치 작성 단계

<설명>

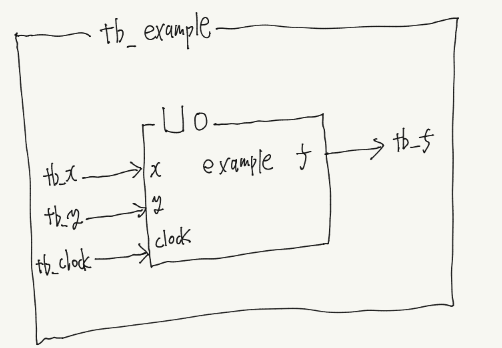

example이라는 모듈을 가정하겠습니다. 이 모듈을 시뮬레이션하려고 합니다.

example의 input으로는 x, y, clock이 있습니다. output으로는 f가 있습니다.

example을 시뮬레이션 하기 위해 상위 모듈 tb_example을 만들었습니다.

tb_example의 tb_x, tb_y, tb_clock 은 example모듈의 input과 각각 연결됩니다.

마찬가지로 tb_f 는 example 모듈의 output과 연결됩니다.

<코드>

`timescale 1ns/1ps //(1) timescale 설정

module tb_example(); //(2) 모듈선언

reg tb_clock; //(3) 입력과 출력 선언

reg tb_x, tb_y;

wire tb_f;

parameter clk_period = 10;

example U0(.clock(tb_clock), .x(tb_x), .y(tb_y), .f(tb_f)); //(4) 모듈 인스턴스화

//example U0(tb_clock, tb_x, tb_y, tb_f);

always begin //(5) clock 생성

tb_clock = 1;

forever #(clk_period/2) tb_clock = ~tb_clock;

end

initial begin //(6) 초기화 및 파형입력

tb_x = 0; tb_y = 0; #10;

tb_x = 1; #10;

tb_x = 1; tb_y = 1; #10;

tb_y = 1; #10;

end

endmodule(1) timescale 설정

시뮬레이션의 시간 간격과 정밀도를 설정합니다. 다음과 같은 형태로 작성합니다.

`timescale (time unit)/(simulation precision)

time unit : 시간의 단위를 결정합니다. #1 즉, delay의 단위를 결정합니다. 예시 코드의 inital 구문 안에 #10은 time unit의 10배의 delay를 나타냅니다.

simulation precison : 시뮬레이션 수행 단위를 나타냅니다. time unit보다 매우 작게 설정하시면 됩니다. 예시 코드

(2) 모듈 선언

테스트하고자 하는 모듈을 선언합니다.

테스트벤치도 하나의 모듈이기 때문에 똑같이 모듈 선언합니다. 하지만 테스트벤치는 input과 output이 없기 때문에, list에 아무 input, output이 없는 형태입니다. 괄호 안이 비어있죠.

(3) 입력과 출력 선언

테스트하고자 하는 Verilog 코드의 input은 reg 형으로, output은 wire 형으로 선언합니다.

(4) 모듈 인스턴스화(instantiation)

테스트하고자 하는 Verilog 코드 내의 모듈을 인스턴스화(instantiation)합니다. 인스턴스화는 테스트할 모듈을 가져오는 작업입니다.

저희가 시뮬레이션할 모듈인 example을 써주시고, 그 옆에 모듈의 이름을 작성해주세요. 다음과 같은 형태입니다.

example U0(…);

포트를 연결하는 방법(괄호를 채우는 방법)은 두 가지가 있습니다. ordered instantiation과 named instantiation입니다.

ordered instantiation : 시뮬레이션 할 모듈에서의 포트 작성 순서를 바탕으로 작성합니다. 순서가 중요합니다. 리스트에는 테스트벤치의 포트를 작성합니다. 다음과 같은 형태입니다.

example U0(tb_clock, tb_x, tb_y, tb_f);

named instatiation : 시뮬레이션 할 모듈의 포트를 직접 인용합니다. named instantiation과 달리 순서는 중요하지 않습니다. 하지만 포트를 알맞게 연결시켜야 합니다. 점(.) 뒤에 모듈의 포트를 적고 괄호 안에는 테스트벤치의 포트를 작성합니다. 다음과 같은 형태입니다.

example U0(.clock(tb_clock), .x(tb_x), .y(tb_y), .f(tb_f));

(5) clock 생성

always 블록을 사용하여 clock을 생성합니다. clock이 필요한 순차회로를 시뮬레이션 할 때 사용합니다.

예시 코드에서 parameter clk_period = 10; 은 clk_period라는 상수 값을 설정한 것 입니다. clock의 주기를 10으로 설정하였습니다.

(6) 초기화 및 파형입력

initial 블록을 사용하여 초기값 및 입력파형을 설정합니다.

#(숫자)를 이용하여 파형입력 사이에 time unit의 숫자 배수 만큼의 delay를 설정할 수 있습니다.

3. Verilog 테스트벤치 작성 방법 – 예시 코드

<JK 플립플롭 테스트벤치>

`timescale 1ns/1ps //(1) timescale 설정

module tb_jk();//(2) 모듈선언

reg clk, j, k; //(3) 입력과 출력 선언

wire Q;

parameter clk_period = 1;

jk U0(.clk(clk), .j(j), .k(k), .Q(Q)); //(4) 모듈 인스턴스화

always begin //(5) clock 생성

clk = 0;

forever #(clk_period/2) clk = ~clk;

end

initial begin //(6) 초기화 및 파형입력

#10 j = 0; k = 1; // reset

#10 j = 1; k = 0; // set

#10 j = 1; k = 1; // toggle

#10 j = 0; k = 0; // reset

end

endmodule

지금까지 Verilog 테스트벤치 작성 방법에 대해 알아보았습니다.

궁금하신 사항이나 오류가 있으면 댓글 달아주세요!

감사합니다